三星 SK 海力士打响 DRAM 架构战

5 月 8 日消息,第七代 DRAM(1d)制程标准角逐已进入白热化阶段,三星与 SK 海力士正式打响架构之战,两大存储巨头争相抢先量产,

力图将自家技术方案确立为下一代 DRAM 行业通用标准。

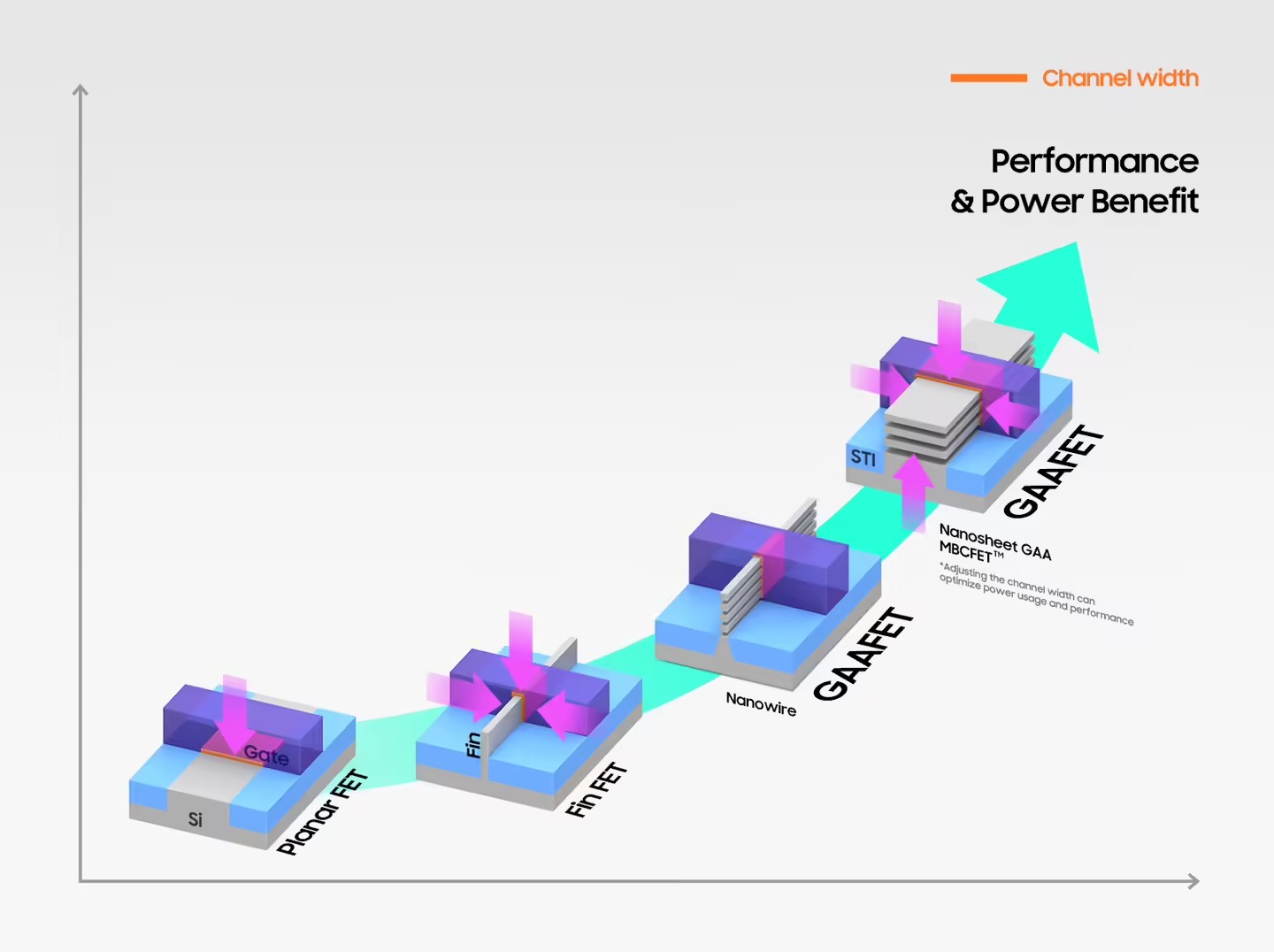

三星主推GAAFET 全环绕栅极晶体管工艺。在逻辑芯片制程中,GAAFET 依靠栅极全包裹沟道,大幅提升电流控制能力;而应用于 DRAM 时,

三星需实现 GAAFET 晶体管与电容在同一存储单元集成。

为此,三星借鉴 NAND 闪存架构思路,将读写控制电路布局在存储阵列底层。三星计划在 2026 年 VLSI 研讨会上,亮相16 层垂直堆叠 DRAM方案,

采用 GAA 晶体管搭配横向放置存储电容的设计。

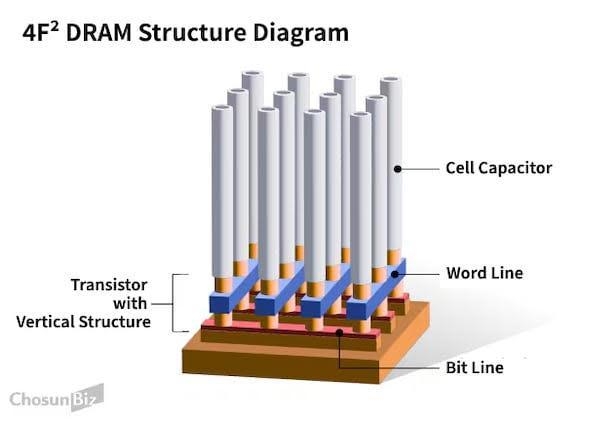

SK 海力士则押注4F² 架构,采用晶体管垂直堆叠方案,同样以栅极材料环绕晶体管结构,并将电容数据接收组件置于晶体管柱下方。

其中 F 为最小特征尺寸,4F² 单元为 2F×2F 正方形布局,对比传统 6F²(3F×2F)设计,芯片面积可缩减约 30%。

早在 2025 年 IEEE VLSI 国际研讨会上,SK 海力士已公布该技术路线,其 4F² 垂直栅极平台主打高密度、高速度、低功耗三大优势,

并现场验证了垂直栅极 DRAM 的电气性能表现。

业内透露,三星已敲定技术规划,拟在第七代 1d nm DRAM 之后导入垂直通道晶体管技术,相关产品最快 2—3 年内落地量产。

SK 海力士同样规划垂直结构 DRAM(含 4F² 架构)三年量产,与三星形成正面时间与技术双线竞争。